1.设计目标

设计基于单口SRAM的转置型FIR,半并行实现,要求满足:

- 并行程度与串行程度参数可配置

- 数据位宽可配置,支持负数,负数为补码类型

2.参数表

| 名称 | 默认值 | 说明 |

|---|---|---|

| PALL_PAM | 4 | 并行阶数 |

| PALL_PAM_LOG | 2 | 并行阶数LOG值 |

| SERI_PAM | 4 | 串行阶数 |

| SERI_PAM_LOG | 2 | 串行阶数LOG值 |

| DATA_WIDTH | 16 | 数据位宽 |

3.端口列表

3.1.系统端口

| 名称 | 类型 | 位宽 | 说明 |

|---|---|---|---|

| clk | input | 1 | 系统时钟 |

| rst_n | input | 1 | 系统复位信号,低有效 |

3.2.配置端口

| 名称 | 类型 | 位宽 | 说明 |

|---|---|---|---|

| cfg_valid | input | 1 | 配置有效信号 |

| cfg_addr | input | PALL_PAM_LOG*SERI_PAM_LOG | 配置地址 |

| cfg_data | input | DATA_WIDTH | 配置数据 |

3.3.数据端口

| 名称 | 类型 | 位宽 | 说明 |

|---|---|---|---|

| din_valid | input | 1 | 输入有效信号 |

| din_busy | output | 1 | 输入忙信号 |

| din_data | input | DATA_WIDTH | 输入数据 |

| dout_valid | output | 1 | 输出有效信号 |

| dout_busy | input | 1 | 输出忙信号 |

| dout_data | output | DATA_WIDTH | 输出数据 |

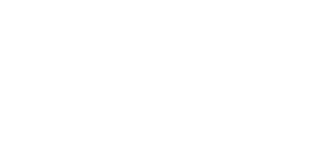

4.系统结构

4.1.结构框图

该FIR共分为四个部分:

- 输入部分:输入寄存器和单口RAM,用于控制输入端口信号,实现数据输入

- 计算部分:由多个串行单元组成,每个串行单元 串行计算,多个串行单元之间并行计算

- 输出部分:输出寄存器,用于控制输出端口信号实现结果输出功能

- 控制部分:产生时序控制信号,控制输入部分、计算部分和输出部分的运行

4.2.系统算法

以一个六阶的FIR为例,并行度为2,串行度为3(每个串行处理单元串行处理3个乘加操作),整体有以下数据流:

可以发现,对于:

而言,前一部分的部分和在PE0的第0~2cycle中计算,后一部分的部分和在PE1的3~5cycle中计算,同时,PE0在第3~5个周期中计算$y(1)$的部分和。因此对于$m \times n$阶的FIR(并行度为m,串行度为n),每个串行单元负责一个FIR结果的n个乘法的计算。对于第i个串行单元,负责$h(j \times m + i),j= 0,1,…,n$和对应输入数据的乘法。现在考虑第k个输出$y(k)$,相关伪代码如下所示:

1 | k_result = 0; |

对于第i个PE(PE的标号计算从1开始),在第j个周期(周期标号从0开始),输出的权值为$h[(n-j) \times m - i]$,每个PE的标号i是固定的,因此ROM对应的地址仅与当前串行周期数有关。对于第z个周期的输入(z计数从0开始,输出$x(k)$的周期为第0周期),对应的输入数据应为$x[k+m\times (z\%n) + z //n]$,因此对于数据RAM取数据的地址除了与周期数z有关外,还与k有关。

5.子模块设计

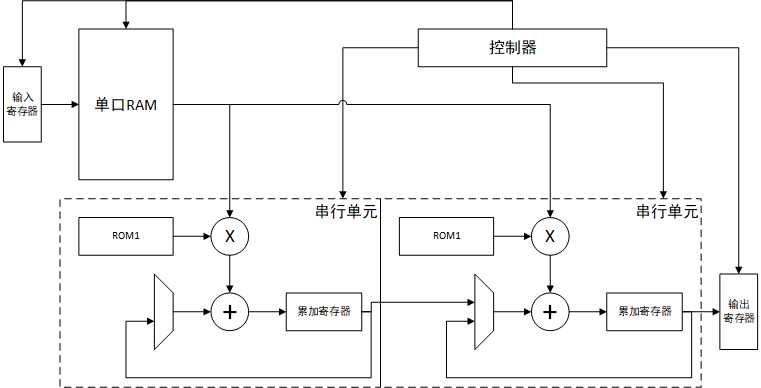

5.1.输入模块

5.1.1.需求

输入模块包括输入数据寄存器和数据RAM,需要实现以下功能:

- 输入寄存器使用P2P接口,当且仅当P2P端口valid信号高且busy信号低时,输入有效

- 数据寄存器中的数据在控制模块的控制下将数据输入到RAM中保存

5.1.2.端口

| 名称 | 类型 | 位宽 | 说明 |

|---|---|---|---|

| clk | input | 1 | 系统时钟 |

| rst_n | input | 1 | 系统复位信号,低有效 |

| din_valid | input | 1 | 输入P2P接口有效信号 |

| din_busy | input | 1 | 输入P2P接口忙信号,控制器生成 |

| din_data | input | DATA_WIDTH | 输入P2P数据信号 |

| control_ram_addr | input | SERL_PRAM_LOG+PALL_PRAM_LOG | 读写数据ram的地址 |

| control_ram_write | input | 1 | 写ram请求信号 |

| unit_din | output | DATA_WIDTH | ram输出数据 |

5.1.3.实现

该部分设计如上图,共两个部分,如下所示:

- 输入寄存器:P2P接口的输入寄存器,P2P接口的busy信号由控制器产生,该寄存器接收valid和busy信号,当valid为高且busy为低时,将输入数据data锁存到输入寄存器中

- RAM:数据单口先读后写RAM,接收控制器的控制信号,写数据从输入寄存器获得,数据输出到内部端口

该部分不包括控制流部分,仅实现输入的数据流,控制流由控制器生成。输出端口的数据来源为RAM或输入寄存器。当执行RAM写入操作时,内部输出数据来源于输入寄存器,否则来源于数据RAM。

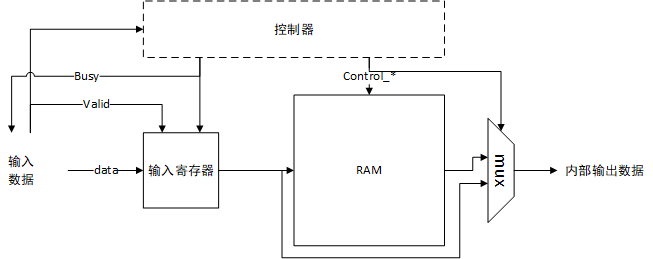

5.2.串行处理单元

5.2.1.需求

串行处理单元,实现串并行处理的串行部分,多个串行处理单元并行实现并行部分,单个单元的需求为:

- 实现串行的相乘相加,一个操作数来自ROM,一个操作数来自输入模块的输出

- 实现可选择的累加,选择控制信号由控制模块生成

5.2.2.端口

| 名称 | 类型 | 位宽 | 说明 |

|---|---|---|---|

| clk | input | 1 | 系统时钟 |

| rst_n | input | 1 | 系统复位信号,低有效 |

| cfg_valid | input | 1 | 配置有效信号,高有效 |

| cfg_addr | input | PALL_PAM_LOG+SERI_PAM_LOG | 配置目标地址 |

| cfg_data | input | DATA_WIDTH | 配置数据 |

| unit_din | input | DATA_WIDTH | 乘法操作数,来自输入模块 |

| unit_partsum_din | input | DATA_WIDTH*2 | 部分和累加操作数,来自上一个串行单元 |

| unit_partsum_dout | output | DATA_WIDTH*2 | 部分和,输出到下一个串行单元 |

| control_rom_addr | input | SERI_PAM_LOG | 参数ROM地址,产生ROM的乘法操作数 |

| control_mux_controller | input | 2 | 控制信号,控制累加器功能 |

5.2.3.实现

串行处理单元如上图所示,该部分仅包括数据流,控制流由控制器统一产生。分为以下几个部分:

- ROM:存储当前单元的相关数据,可使用

cfg_*接口进行参数配置。非配置时根据控制器提供的地址输出乘法操作数 - 乘法器:带符号数乘法器,将ROM的数据输出和数据输入

unit_din进行相乘 - 累加部分:包括累加寄存器、加法器和Mux,可选择不执行操作、乘法结果与部分和输入相加和乘法结果累加三种操作

对于一次操作,数据输入和ROM地址对应的数据输出到乘法器完成乘法,根据控制信号加法器将乘法结果与部分和输入或累加结果进行相加,累加寄存器的值输出到部分和输出端口。其中的reg用于保证数据对齐。

5.3.控制器

5.3.1.需求

该设计使用中央控制的方式进行控制,所有控制信号均由控制器生成,包括:

- 控制输入部分的busy信号和数据RAM的地址

- 控制串行处理单元的ROM地址和操作方式

- 控制输出部分的valid信号

5.3.2.端口

| 名称 | 类型 | 位宽 | 说明 |

|---|---|---|---|

| clk | input | 1 | 系统时钟 |

| rst_n | input | 1 | 系统复位,低有效 |

| din_valid | input | 1 | 输入数据P2P端口有效信号 |

| din_busy | output | 1 | 输入数据P2P端口忙信号 |

| control_ram_addr | output | SERL_PRAM_LOG+PALL_PRAM_LOG | 读写数据ram的地址 |

| control_ram_write | output | 1 | 写数据ram请求信号 |

| control_rom_addr | output | SERI_PAM_LOG | 参数ROM地址,产生ROM的乘法操作数 |

| control_mux_controller | output | 2 | 控制信号,控制累加器功能 |

| dout_busy | input | 1 | 输出数据P2P端口忙信号 |

| dout_valid | output | 1 | 输出数据P2P端口有效信号 |

5.3.3.实现

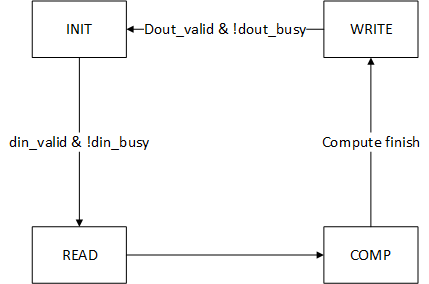

该部分的核心是一个状态机,该状态机控制所有部件的运行,状态机的流程图如下所示:

该状态机有四个状态:

- INIT:初始待机状态,等待输入数据

- READ:读取数据状态,当输入P2P传输发生时从INIT进入,下一时钟周期进入COMP状态

- COMP:计算状态,从READ状态进入,SERI_PAM个时钟周期后进入WRITE状态

- WRITE:输出状态,从COMP状态进入,3个时钟周期(等待计算全部完成)后控制P2P输出端口输出数据

5.3.3.1.输入端口控制实现

输入P2P端口需要控制的信号是din_busy信号,该信号仅在状态机状态为INIT时为低,否则为高。

输入部分RAM地址的控制信号为$k+i\times PALL_PAM,i<SERI_PAM$,其中:

- k为基地址寄存器,每次WRITE状态结束时加1,范围为0~(PALL_PAM+SERI_PAM + 1)

- i为偏移量,在COMP状态中每时钟周期加1,范围为0~SERI_PAM

输入部分RAM写请求信号在COMP的最后一个周期拉高,将数据写入RAM,同时将输入寄存器的值作为数据输出

5.3.3.2.串行处理单元控制实现

串行处理单元的ROM地址信号在COMP状态从SERI_PAM-1到0递减,每时钟周期减1

串行处理单元的MUX控制信号如下所示:

- 在非COMP状态下为0,即加法器不工作

- 在COMP的第一个时钟周期为1,为加法器实现乘法结果与部分和输入相加

- 在COMP的其他时钟周期为3,为加法器实现乘法结果的累加操作

5.3.3.3.输出端口控制实现

输出部分控制信号为dout_valid,在进入WRITE状态3个时钟周期后将该信号拉高,退出WRITE状态时拉低